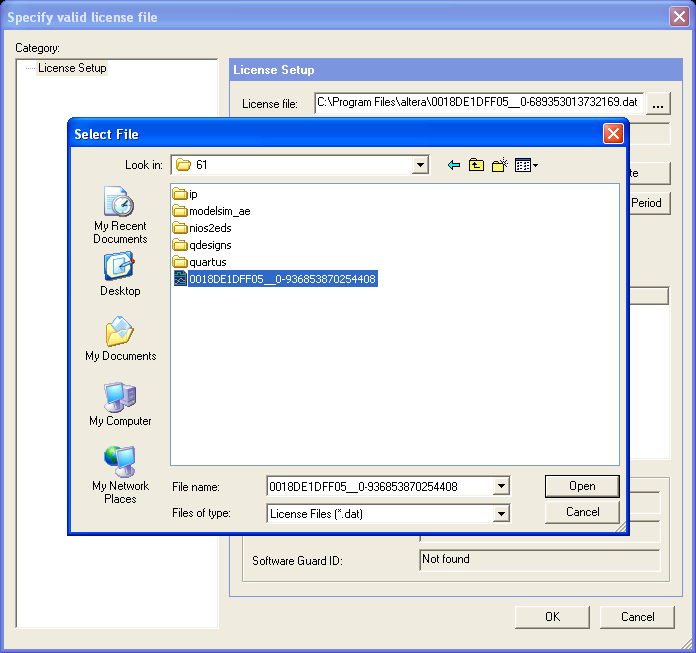

Figure 6 shows the screen captureįigure 6. This is done by selecting Processing > Generate functional Simulation Netlist. Pleaseįollow the steps shown in part I of this tutorial.īefore running functional simulation, a functional simulation netlist for the synthesized circuit needs to be generated. Having successfully compiled our design file, we need a vector waveform file to simulate out design file. The following figures illustrate theĬommand and also the out of the partial compilation.įigure 4. We could run partial compilation by selecting Start Analysis and ElaborationĬommand to check Decoder_2_to_4 file for syntax and semantics error.

Altera quartus ii for students full#

It is possible to run the full compilation or run individual module (Analysis & Synthesis, Compiler will processĭecoder_2_to_4 file. Having saved VHDL file, we need to compile the design file for simulation. As shown in the following figure VHDL file has been saved as Decoder_2_to_4. Please note that VHDL file name has to be the same as the entity

Altera quartus ii for students code#

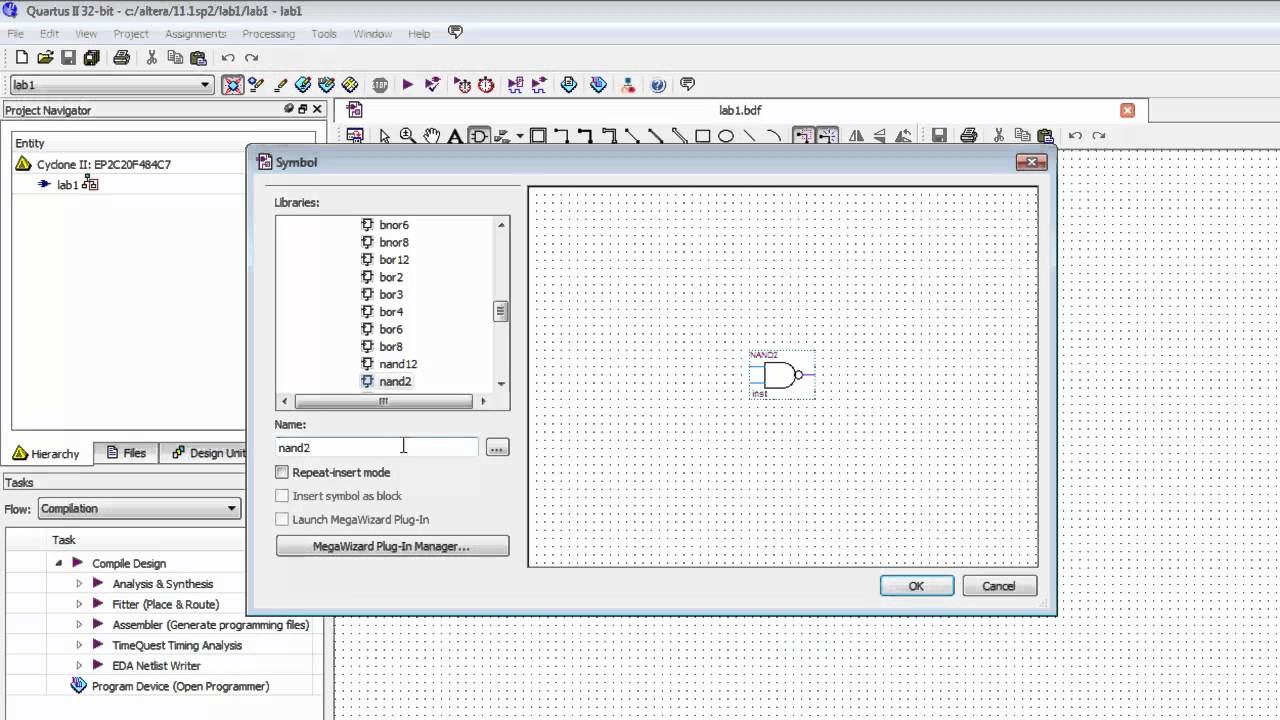

The VHDL code for 2-to -4 decoder in the window. Once we choose VHDL file, Quartus II will open a text editor file vhdl1 to put our design file. HDL based design entry in Quartus II follows most of the steps mentioned in first part for schematic based design.Īfter opening a new project using new project wizard we will choose VHDL design file by clicking

circuit configuration and VHDL code for an 2-to-4 decoder Use ieee.std_logic_1164 - specify which package in the library toĪrchitecture DECODER of Decoder_2_to_4 isįigure 1. The circuit configuration and VHDL code for an 2-to -4 decoder are shown below Please note that VHDL syntax and semantics are beyond the scope of this In this section, a new HDL project containing an 2- to -4 decoder will be designed and compiled with Quartus® II.ĭesign file will be written in VHDL. Creating HDL Design Projects with Quartus II Please note that this tutorial is based on Altera Quartus® II 8 web edition version.ģ. Of simulation, namely, functional simulation and timing simulations, to assess the behavior and performance of the This tutorial will also introduce two types HDL design files are used to synthesize and simulate the desired design.

Quartus® II tutorial is aimed at introducing HDL based design entry method. (HDLs) provides standard text based expressions of the structure and behavior of digital circuits. It becomes veryĭifficult to use this method for a large design with hundreds of primitive gates. Altera Quartus II Tutorial Part II (For ECE 465 Students at UIC) Sajjad Rahaman TA for ECE 465, Spring 2009 Department of Electrical and Computer Engineering University of Illinois at Chicago first part of Quartus® II tutorial illustrates schematic diagram based entry for the desired circuit.

0 kommentar(er)

0 kommentar(er)